# 1. Introducción

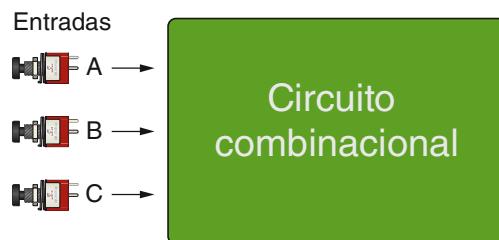

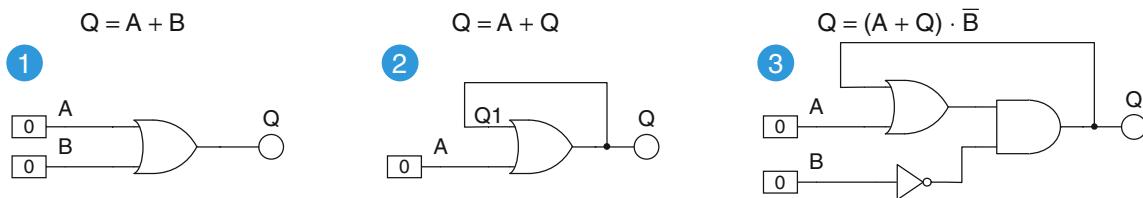

En electrónica digital, podemos diferenciar dos tipos de circuitos: los denominados circuitos combinacionales y los circuitos secuenciales.

En los circuitos combinacionales, que en parte ya se han estudiado en la unidad anterior, el estado de las salidas depende única y exclusivamente del estado de las entradas. Sin embargo, en los circuitos secuenciales, los valores de las salidas dependen de ellas mismas, además del de las entradas.

Figura 10.1. Circuito combinacional.

Figura 10.2. Circuito secuencial.

## Recuerda

Se puede decir que un circuito secuencial tiene memoria, y uno combinacional no.

En esta unidad, se estudiarán de forma básica algunos de los circuitos combinacionales y secuenciales más significativos.

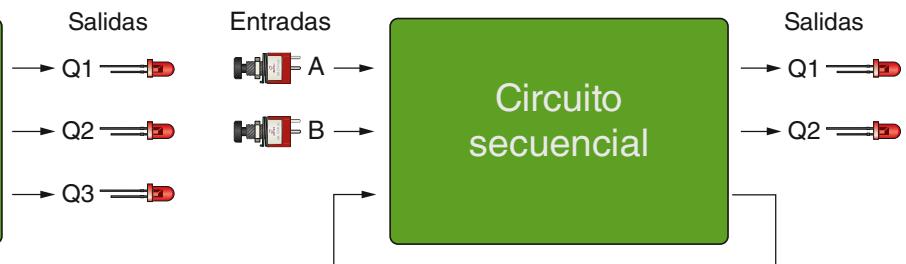

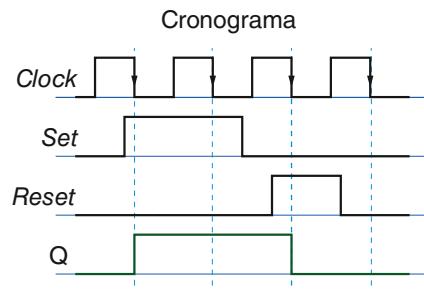

## 1.1. Cronograma

Un cronograma es un gráfico en el que se muestra cómo evolucionan una o más señales, en este caso digitales, en función del tiempo. También recibe el nombre de diagrama de tiempo.

Los cronogramas son especialmente útiles para mostrar el funcionamiento tanto de los circuitos combinacionales como de los secuenciales, y a menudo son utilizados por los fabricantes en las hojas de características para mostrar el comportamiento de sus componentes.

Figura 10.3. Ejemplo de cronograma de una función lógica AND.

En los cronogramas, las señales digitales se muestran con dos posibles valores, el 0 y el 1. Así, el flanco que pasa de 0 a 1 se denomina **flanco ascendente** o de subida, y el que pasa de 1 a 0 se denomina **flanco descendente** o de bajada.

Es importante identificar los dos tipos de flanco, ya que muchos circuitos digitales secuenciales funcionan basándose en ellos.

Figura 10.4. Flancos de una señal digital.

## 2. Circuitos combinacionales

### Recuerda

En los circuitos combinacionales con codificadores/decodificadores y multiplexores/demultiplexores, se suelen utilizar diferentes símbolos para identificar las entradas (E, I, D, etc.) y para las salidas (S, A, Q, X, etc.).

Aquí se utilizará I para las entradas y Q para las salidas.

Los circuitos combinacionales más característicos son:

- Los codificadores y decodificadores.

- Los multiplexores y demultiplexores.

Todos ellos se pueden montar mediante circuitos de puertas lógicas, pero, para facilitar el diseño y su integración en los circuitos electrónicos digitales, se comercializan también en formato de circuito integrado.

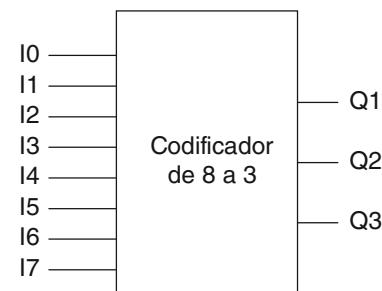

### 2.1. El codificador

Es un circuito combinacional que permite obtener en su salida un número codificado en binario, partiendo de una serie de entradas no codificadas.

Los codificadores disponen de  $2^n$  entradas y un número,  $n$ , determinado de salidas. Así, un codificador de 2 salidas, dispone de  $2^2 = 4$  entradas, uno de 3 salidas  $2^3 = 8$  entradas, y así sucesivamente. A los decodificadores se les suele denominar también con un código numérico, cuya relación se encuentra entre el número de entradas y el número salidas:  $4 \times 2$ ,  $8 \times 3$ ,  $16 \times 4$ , etc.

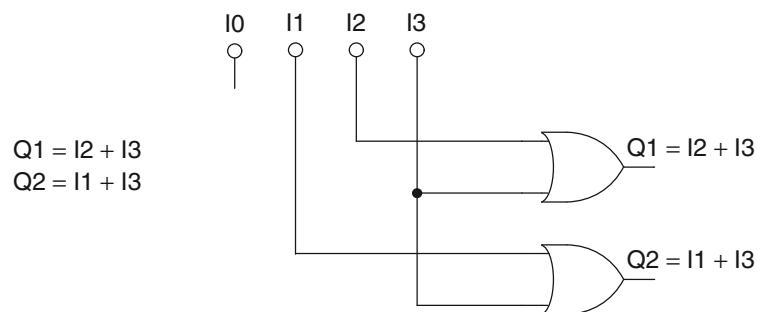

En el siguiente ejemplo se muestra un codificador de 4 entradas a 2 bits de salida. En él, si las entradas se activan individualmente, el resultado en las salidas corresponde con su número codificado en binario.

Así, si analizamos la tabla de la verdad del codificador, se observa que las salidas Q1 y Q2 se activan en función de las siguientes combinaciones lógicas de las entradas y, por tanto, es posible representar su circuito equivalente.

| Entradas |    |    |    | Salidas |    | Número en decimal |

|----------|----|----|----|---------|----|-------------------|

| I0       | I1 | I2 | I3 | Q1      | Q2 |                   |

| 1        | 0  | 0  | 0  | 0       | 0  | 0                 |

| 0        | 1  | 0  | 0  | 0       | 1  | 1                 |

| 0        | 0  | 1  | 0  | 1       | 0  | 2                 |

| 0        | 0  | 0  | 1  | 1       | 1  | 3                 |

Figura 10.5. Codificador de 2 bits de salida y tabla de la verdad.

### Saber más

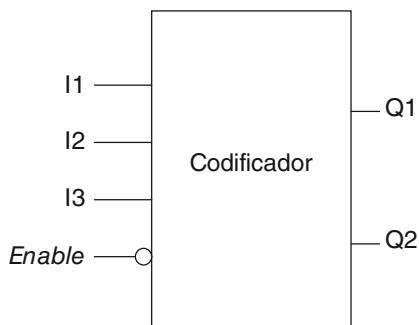

Por lo general, la entrada de habilitación es de tipo negada, ya que, de esta forma, aunque no se conecte el circuito, este puede funcionar igualmente.

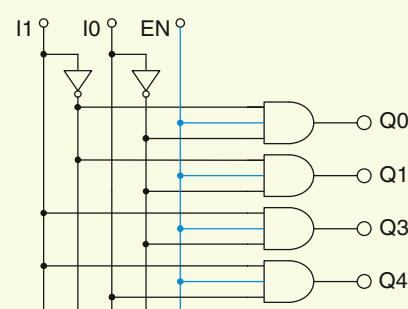

Figura 10.6. Entrada enable negada.

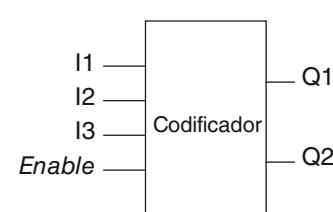

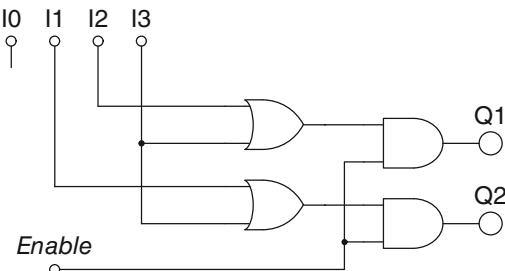

En los circuitos digitales es habitual disponer de una entrada denominada *enable*, mediante la cual es posible habilitar o deshabilitar la actuación sobre las salidas si se aplica en ella un determinado nivel lógico. En el caso del ejemplo del codificador  $4 \times 2$ , su implementación se realiza añadiendo puertas AND a cada una de las salidas de las puertas OR y conectando en uno de sus terminales la entrada de habilitación. Así, si la entrada *enable* no se encuentra a valor lógico "1", las salidas estarán desactivadas o deshabilitadas.

Figura 10.7. Codificador de 2 bits de salida con entrada de habilitación.

A continuación, se muestra un codificador de 8 bits de entrada a 3 de salida, en cuya tabla de la verdad se observa como en función de número de la entrada activada se obtienen en las salidas su correspondiente número en binario.

| I0 | I1 | I2 | I3 | I4 | I5 | I6 | I7 | Q1 | Q2 | Q3 | Número |

|----|----|----|----|----|----|----|----|----|----|----|--------|

| 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0      |

| 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1      |

| 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 2      |

| 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 3      |

| 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 0  | 0  | 4      |

| 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 1  | 0  | 1  | 5      |

| 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 1  | 0  | 6      |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 1  | 7      |

Tabla 10.1. Tabla de la verdad del codificador de 8 bits de entrada a 3 de salida.

Si se escriben las ecuaciones lógicas para las situaciones en las que el resultado en las salidas es 1, se puede dibujar el circuito combinacional equivalente.

Como ya se ha visto en el ejemplo anterior, los codificadores se pueden construir conectando puertas lógicas entre sí, pero es más habitual utilizarlos en formato de circuito integrado, ya que facilita el diseño e implementación de circuitos.

Los codificadores pueden ser de dos tipos: con prioridad o sin prioridad.

### 2.1.1. Codificadores sin prioridad

Son codificadores que están diseñados para mantener activa una sola de sus entradas. En el caso de que exista más de una, el resultado en las salidas se suma, generando un cierto desorden y confusión, ya que el resultado puede ser el no deseado.

Por ello, el diseño del circuito previo al codificador debe hacerse de tal forma que no sea posible poner a nivel lógico alto más de una entrada a la vez.

Así, si en el circuito de codificador de  $8 \times 3$  mostrado anteriormente nos encontramos con dos entradas activadas simultáneamente, por ejemplo, la I3 y la I4, el resultado en las salidas es la suma de las dos.

| I0                       | I1 | I2 | I3 | I4 | I5 | I6 | I7 | Q1  | Q2 | Q3 | Número |

|--------------------------|----|----|----|----|----|----|----|-----|----|----|--------|

| ...                      |    |    |    |    |    |    |    | ... |    |    | ...    |

| 0                        | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0   | 1  | 1  | 3      |

| 0                        | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 1   | 0  | 0  | 4      |

| ...                      |    |    |    |    |    |    |    | ... |    |    | ...    |

| Resultado en las salidas |    |    |    |    |    |    |    | 1   | 1  | 1  |        |

Tabla 10.2. Codificador de 8 bits de entrada a 3 de salida con 2 entradas activadas.

## Actividades

1. Utilizando un software de simulación electrónica, dibuja el circuito combinacional del codificador de  $8 \times 3$  y realiza lo siguiente:

- Comprueba el funcionamiento del circuito, conectando lámparas de prueba en cada una de las salidas del circuito, y observa el número en binario formado por ellas.

- Comprueba lo que ocurre con el resultado en las salidas cuando se activa más de una entrada a la vez.

- Implementa una entrada enable en el circuito y comprueba si el funcionamiento es correcto. ¿Qué tendría que hacer para que esta entrada habilite el funcionamiento de las salidas cuando su valor lógico es 0? Pruébalo también.

## Saber más

Ecuaciones lógicas para el codificador de 8 de entrada y 3 de salida.

$$Q1 = I4 + I5 + I6 + I7$$

$$Q2 = I2 + I3 + I6 + I7$$

$$Q3 = I1 + I3 + I5 + I7$$

Figura 10.8. Codificador de 8 entradas y 3 salidas.

## Saber más

A la entrada de habilitación, enable, también se la denomina strobe.

### 2.1.2. Codificadores con prioridad

Son codificadores que resuelven el problema de los codificadores sin prioridad cuando se encuentra activada más de una entrada. En estos, si se da la situación de que dos o más entradas están a nivel lógico alto, el valor codificado en las salidas es el correspondiente a la entrada de mayor prioridad o mayor valor numérico.

En la tabla de la verdad se representan con una X los valores de las entradas que resultan irrelevantes. De esta forma, si, por ejemplo, se encuentran activadas dos o más entradas a la vez, el resultado en las salidas solamente es el de mayor prioridad.

| I0 | I1 | I2 | I3 | I4 | I5 | I6 | I7 | Q1 | Q2 | Q3 | Número |                 |

|----|----|----|----|----|----|----|----|----|----|----|--------|-----------------|

| 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0      | Menor prioridad |

| x  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1      |                 |

| x  | x  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 2      |                 |

| x  | x  | x  | 1  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 3      |                 |

| x  | x  | x  | x  | 1  | 0  | 0  | 0  | 1  | 0  | 0  | 4      |                 |

| x  | x  | x  | x  | x  | 1  | 0  | 0  | 1  | 0  | 1  | 5      |                 |

| x  | x  | x  | x  | x  | x  | 1  | 0  | 1  | 1  | 0  | 6      |                 |

| x  | x  | x  | x  | x  | x  | x  | 1  | 1  | 1  | 1  | 7      | Mayor prioridad |

Tabla 10.3. Tabla de la verdad de un codificador con prioridad.

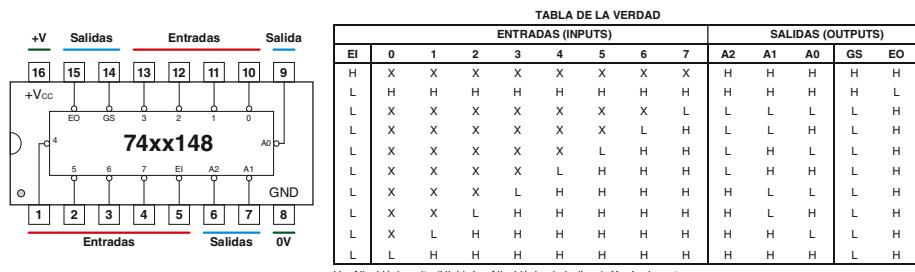

### Codificador con prioridad 74xx148

El circuito integrado 74xx148 es un codificador con prioridad de 8 entradas a 3 salidas. En él, tanto las entradas como las salidas están negadas, por lo tanto, trabajan con niveles lógicos bajos, es decir de 0 lógico. Dispone de una entrada de habilitación EI, y dos salidas adicionales: EO que permite conectar en cascada el integrado con otros del mismo tipo, y GS que indica con valor alto cuando todas las salidas están a 1.

A continuación, se muestra la tabla de la verdad representada en su hoja de características (data sheet). En ella el valor 1 se muestra con H (high), el valor 0 con L (low) y cuando el valor lógico es irrelevante, se muestra con X.

Figura 10.9. Pineado y tabla de la verdad del circuito integrado 74xx148.

## Actividades

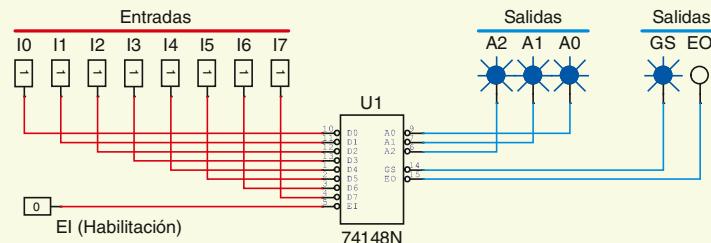

2. Utilizando un software de simulación electrónica, comprueba la tabla de la verdad del codificador con prioridad 74xx148. Para ello, conecta interruptores lógicos a las entradas, y lámparas de prueba a las salidas.

Debes tener en cuenta que tanto unas como otras están negadas, y para habilitar las salidas es necesario que la entrada EI esté a nivel lógico bajo, es decir, a 0 lógico.

Figura 10.10. Montaje para simular.

## 2.2. El decodificador

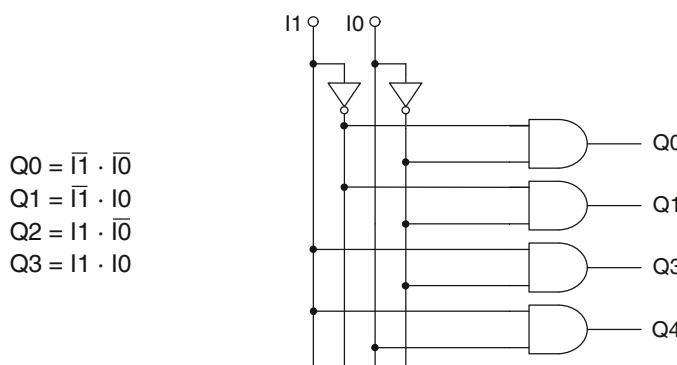

Es un circuito combinacional que funciona a la inversa del codificador. En este caso, a las entradas se les aplica un número en binario, activando la salida correspondiente al número codificado en ellas. Un decodificador tiene un número  $n$  de bits de entradas, con los que se codifica un número en binario, y número  $2^n$  de salidas de datos, las cuales se activan en función del número codificado en las entradas.

Así, si se desea obtener cuatro líneas de datos, es necesario codificar un número en binario de 2 bits.

En la siguiente tabla de la verdad, se muestra cómo, al codificar en binario las entradas, se activa el número de salida correspondiente, no siendo posible activar más de una salida a la vez.

| Número | Entradas |    | Salida |    |    |    |

|--------|----------|----|--------|----|----|----|

|        | I1       | I0 | Q3     | Q2 | Q1 | Q0 |

| 0      | 0        | 0  | 0      | 0  | 0  | 1  |

| 1      | 0        | 1  | 0      | 0  | 1  | 0  |

| 2      | 1        | 0  | 0      | 1  | 0  | 0  |

| 3      | 1        | 1  | 1      | 0  | 0  | 0  |

Tabla 10.4. Tabla de la verdad de un decodificador binario.

Así, el resultado lógico de cada salida corresponde con el término mínimo de la fila en la que se encuentra. Por lo tanto, las ecuaciones y el circuito lógico para cada una de ellas son los mostrados a continuación:

Figura 10.11. Ecuaciones lógicas y circuito de un codificador de 2 a 4 con puertas lógicas.

La entrada de habilitación (*enable*) se consigue conectando una tercera entrada a cada una de las puertas AND. Así, si esta no se encuentra a 1 lógico, no es posible activar ninguna de las salidas.

### Actividades

3. Utilizando un software de simulación electrónica, comprueba el funcionamiento del decodificador de 2 entradas a 4 salidas de la figura.

Diseña el circuito de tal forma que disponga de una entrada de habilitación (*enable*) y comprueba su funcionamiento.

¿Qué es necesario hacer para que la entrada de habilitación funcione con lógica negativa? Simúlalo y comprueba su funcionamiento.

¿Es posible conseguir que más de una salida esté activa a la vez? ¿Por qué?

### Vocabulary

- Flanco positivo: positive edge.

- Flanco negativo: negative edge.

- Flanco ascendente: rising edge.

- Flanco descendente: falling edge.

- Señal de reloj: clock signal.

- Puerta lógica: logic gate.

- Biestable: latch, flip-flop.

- Lógica secuencial: sequential logic.

- Comutación: switching.

- Rebote: rebound.

- Retardo: delay.

- Exceso: overage.

- Codificador: encoder.

- Decodificador: decoder.

- Nivel alto: high level.

- Nivel bajo: low level.

- Irrelevante: irrelevant.

- Comutador: toggle.

- Contador: counter.

- Arriba: up.

- Abajo: down.

- Síncrono: synchronous.

- Asíncrono: asynchronous.

Figura 10.12. Circuito lógico para simular.

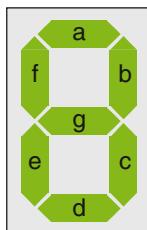

## Recuerda

El orden de los segmentos LED de un *display* es el siguiente:

Figura 10.13. Segmentos de un display.

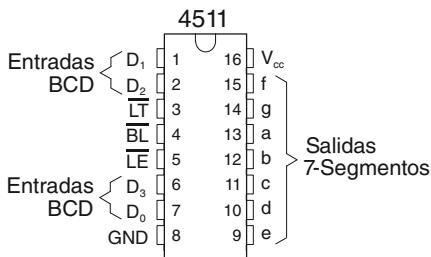

## Saber más

Un circuito de similares características al 74xx48, en tecnología CMOS, es el CD4511. Se trata de un codificador BCD a un display de 7 segmentos LED en cátodo común.

Figura 10.14. Pineado del circuito integrado CD4511.

### 2.2.1. Decodificador BCD para *display* de 7 segmentos

Es un decodificador especialmente diseñado para convertir un número en código BCD y mostrarlo directamente en un *display* de 7 segmentos. A diferencia del codificador mostrado en el ejemplo anterior, en este caso, cada vez que se ponen a 1 lógico las entradas para formar un número en BCD, se activan varias salidas a un mismo tiempo, excitando los segmentos LED necesarios del *display* y así formar el número correspondiente.

Los CI 74xx47 y 74xx48 permiten realizar este tipo de codificación. Ambos funcionan de forma similar, pero se diferencian en que el primero se utiliza para *displays* que tienen ánodo común y el segundo para los que tienen el cátodo común. Ambos disponen de 4 entradas para la codificación BCD y 7 salidas para conectar cada uno de los segmentos LED del *display*. Además, tienen 3 entradas auxiliares, que internamente están negadas, de las cuales, la denominada LT es de gran utilidad, ya que permite comprobar si los segmentos LED del *display* son correctos.

A continuación, se muestra la tabla de la verdad del circuito integrado 74xx47 y el resultado para las diferentes combinaciones BCD.

| Número en decimal | ENTRADAS |   |   |   | SALIDAS |   |   |   |   |   |   |

|-------------------|----------|---|---|---|---------|---|---|---|---|---|---|

|                   | D        | C | B | A | a       | b | c | d | e | f | g |

| 0                 | L        | L | L | L | L       | L | L | L | L | L | H |

| 1                 | L        | L | L | H | H       | L | L | H | H | H | H |

| 2                 | L        | L | H | L | L       | L | H | L | L | H | L |

| 3                 | L        | L | H | H | L       | L | L | L | H | L | L |

| 4                 | L        | H | L | L | H       | L | H | L | H | L | L |

| 5                 | L        | H | L | H | L       | H | L | L | H | L | L |

| 6                 | L        | H | H | L | H       | H | L | L | L | L | L |

| 7                 | L        | H | H | H | L       | H | H | H | L | H | H |

| 8                 | H        | L | L | L | L       | L | L | L | L | L | L |

| 9                 | H        | L | L | H | L       | L | H | L | L | L | H |

| 10                | H        | L | H | L | H       | H | L | H | L | H | L |

| 11                | H        | L | H | H | H       | H | H | H | H | H | L |

| 12                | H        | H | L | L | H       | L | H | L | L | H | L |

| 13                | H        | H | L | H | L       | H | L | L | H | L | L |

| 14                | H        | H | H | L | H       | H | L | L | L | H | L |

| 15                | H        | H | H | H | H       | H | H | H | H | H | H |

Tabla de la verdad

Resultados en el *display* para cada codificación BCD

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

Símbolo

Pineado

74LS47

IC1

74LS47

Figura 10.15. Tabla de la verdad, símbolo e identificación de terminales del integrado 74LS74.

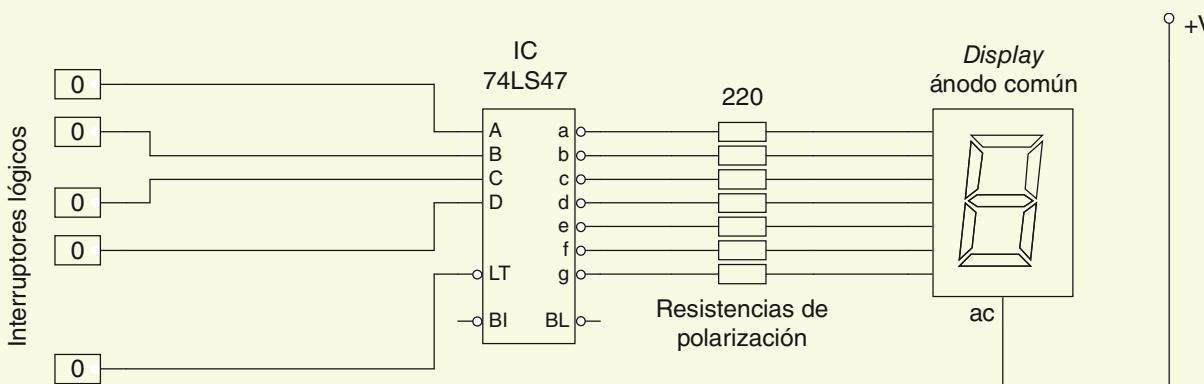

## Actividades

- Utilizando un software de simulación electrónica, monta el circuito de la figura con el circuito integrado 74LS47, un decodificador BCD a 7 segmentos LED. Conecta a sus entradas interruptores lógicos y a sus salidas un *display* de 7 segmentos LED en ánodo común. Comprueba la codificación en BCD de las entradas y observa si el resultado en el *display* se corresponde con la tabla de la verdad. ¿Qué ocurre cuando la entrada LT cambia de nivel lógico?

Figura 10.16. Circuito para simular con el codificador 74LS47.

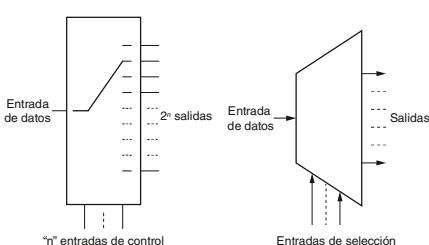

## 2.3. Multiplexor

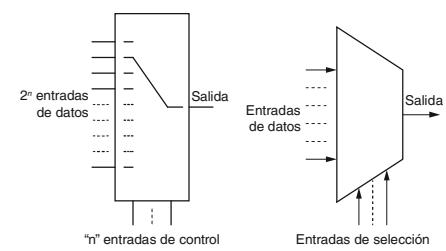

Es un circuito combinacional con un número determinado de entradas de datos y una sola salida.

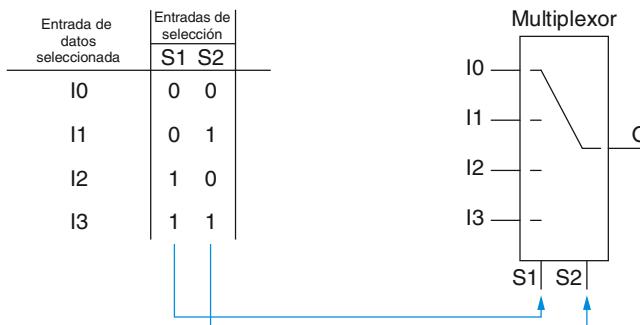

Un multiplexor es un conmutador en el que el estado de uno de los canales de los datos de entrada se transfiere a su salida, en función del valor seleccionado en las denominadas entradas de control o selección.

Así, si  $n$  es el número de canales de control,  $2^n$  es el número de entradas que dispone el multiplexor.

Por tanto, la representación de un multiplexor de 4 entradas de control dispone de 8 entradas de datos. En este caso, el número en binario codificado en las entradas de selección comuta el valor del número de entrada a la salida del multiplexor.

Figura 10.19. Multiplexor de 4 entradas de datos y 2 de selección.

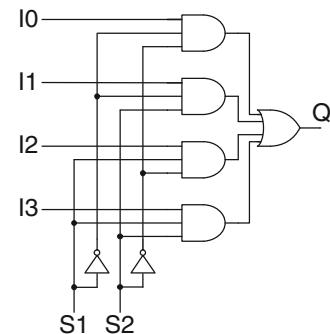

Los multiplexores se pueden configurar mediante circuitos basados en puertas lógicas. No obstante, también se comercializan en formato de circuito integrado facilitando así su conexión e integración en los circuitos digitales. Estos suelen disponer, además de las entradas de datos y de selección, de una entrada de habilitación como la ya estudiada en otros circuitos integrados combinacionales.

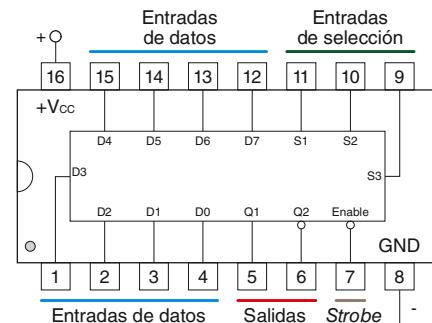

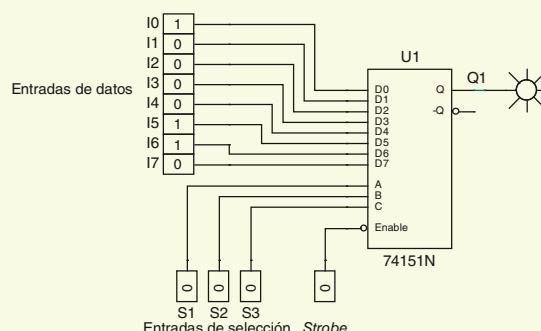

### 2.3.1. Circuito integrado 74151

Un circuito integrado multiplexor ampliamente utilizado es el modelo 74151. Se trata de un multiplexor con 3 entradas de selección y, por tanto, 8 entradas de datos. Dispone de una entrada de habilitación (Pin 7), además de una salida negada o invertida.

Figura 10.17. Representación genérica de un multiplexor.

Figura 10.18. Circuito con puertas lógicas de un multiplexor de 4 entradas de datos y 2 entradas de control.

Figura 10.20. Pineado del circuito integrado 74151.

## Actividades

5. Utilizando un software de simulación electrónica, monta el circuito de la figura con el circuito integrado multiplexor 74151. Conecta a cada una de las entradas de datos sus correspondientes interruptores lógicos y da en ellos varios valores lógicos aleatorios. Commuta las entradas de selección y comprueba que el dato que aparece en la salida corresponde con el valor lógico de la entrada correspondiente.

|    | A | B | C |

|----|---|---|---|

| D0 | 0 | 0 | 0 |

| D1 | 0 | 0 | 1 |

| D2 | 0 | 1 | 0 |

| D3 | 0 | 1 | 1 |

| D4 | 1 | 0 | 0 |

| D5 | 1 | 0 | 1 |

| D6 | 1 | 1 | 0 |

| D7 | 1 | 1 | 1 |

Figura 10.21. Circuito para simular con CI 74151.

Figura 10.22. Representación genérica de un demultiplexor.

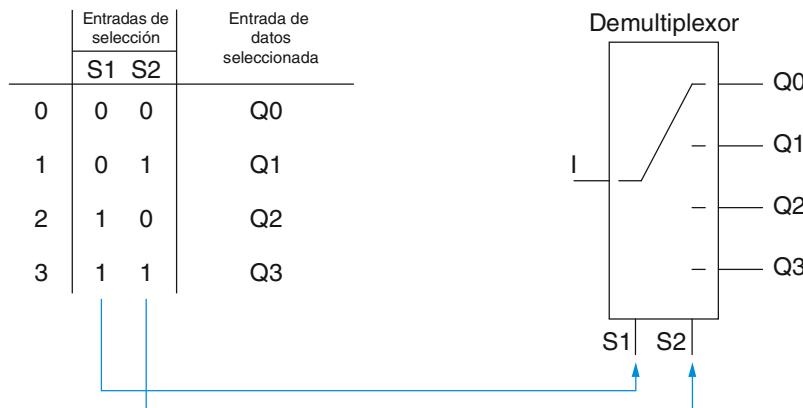

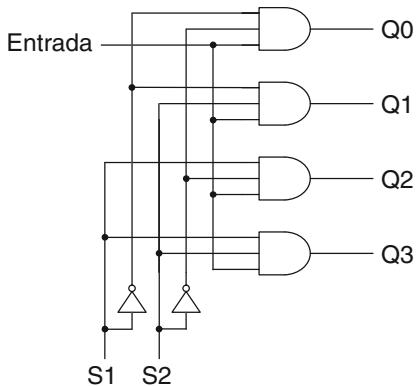

## 2.4. Demultiplexor

Es un circuito combinacional que funciona de forma inversa al multiplexor. Dispone de una única entrada de datos, varias entradas selectoras o de control y un número determinado de salidas. La relación del número de salidas respecto a las entradas de control es de  $2^n$ , siendo  $n$  el número de entradas selectoras.

Así, el funcionamiento del demultiplexor es similar al del multiplexor, pero con sentido inverso en el intercambio de la información. Es decir, el nivel lógico que se presenta en su entrada es trasladado al número de línea de salida, que se ha codificado en binario mediante las entradas selectoras.

Figura 10.23. Demultiplexor de 4 salidas de datos y 2 de control.

Figura 10.24. Circuito con puertas lógicas de un demultiplexor de 4 salidas de datos y 2 entradas de control.

Con un multiplexor es posible convertir en paralelo una información que se recibe en serie.

Muchos circuitos integrados decodificadores pueden ser utilizados como demultiplexores.

## 3. Circuitos secuenciales

En la lógica secuencial, a diferencia de la lógica combinacional, el estado de las salidas no depende exclusivamente de las entradas, sino que también depende de los estados anteriores de sus propias salidas.

Así, una primera aproximación a la lógica secuencial es el que se describe a continuación.

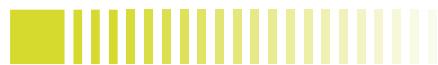

Supóngase la operación OR de dos señales de entrada (1), en el que el resultado lógico de la salida es 1 cuando cualquiera de ellas lo es también. Si una de las señales de entrada se sustituye por la señal de la propia salida de la función (2), cuando la entrada tiene valor 1, la salida se pone a nivel alto y, por tanto, se aplica un 1 lógico en el otro terminal de la puerta OR. De esta forma, la salida se mantiene activada de forma permanente, a pesar de que la entrada que provocó esta acción deje de estar a nivel alto en la puerta lógica. Con esto, se consigue hacer una función de realimentación y así memorizar el estado de la propia salida, aplicando su nivel lógico como si fuese una entrada.

Figura 10.25. Circuito con memoria.

Dicha operación no tiene demasiado sentido si no es posible desactivar el nivel lógico de la salida de alguna manera. Para ello, simplemente se realiza una operación AND de una entrada negada con la operación OR anterior (3), de forma que dicha entrada se utiliza para poner a valor de 0 lógico la salida y desactivar así la realimentación.

De esta forma, si una entrada activa la salida, se mantiene en ese estado, aunque cese la acción sobre ella; y la otra la desactiva, manteniéndola en ese estado, aunque su valor lógico retorne a 0.

Figura 10.26. Secuencia de funcionamiento de un circuito con realimentación.

Por tanto, en el caso de la figura, se puede decir que la entrada A es la activación o SET, y la entrada B es la desactivación o RESET.

Esta forma de realizar circuitos con memoria no es muy utilizada en electrónica digital, pero está justificado su estudio para comprender el concepto de realimentación. Una forma más eficiente de implementar circuitos secuenciales es utilizar los denominados biestables, bien configurándolos a base de puertas lógicas o bien en formato de circuito integrado específicamente diseñado para tal efecto.

### 3.1. El biestable

Un biestable es un circuito electrónico que tiene dos posibles estados estables. Se puede decir que un biestable es un circuito con memoria, que permite almacenar un dato en binario y utilizarlo cuando sea necesario en el circuito en el que se encuentra implementado.

Los biestables también se conocen con sus denominaciones del inglés *flip-flop* o *latch*.

En función de si la comutación de sus salidas atiende o no a una señal de reloj (*clock*), los biestables se pueden clasificar en:

- **Biestables asíncronos:** son aquellos en los que la señal de salida cambia cuando se producen variaciones lógicas en sus entradas.

- **Biestables síncronos:** son aquellos en los que la activación de la salida cambia no solo cuando se producen cambios lógicos en sus entradas, sino que también depende del estado de una señal de sincronismo, denominada de reloj o *clock*.

### Saber más

La combinación de biestables permite formar otro tipo de circuitos: son los contadores o registros de desplazamiento. Los contadores se estudiarán en esta unidad.

Figura 10.27. Tren de pulsos de una señal de reloj digital.

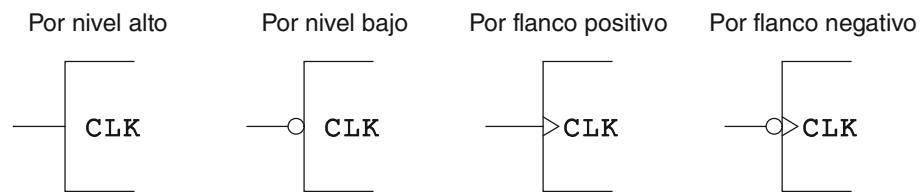

### 3.1.1. Forma de disparo de los biestables síncronos

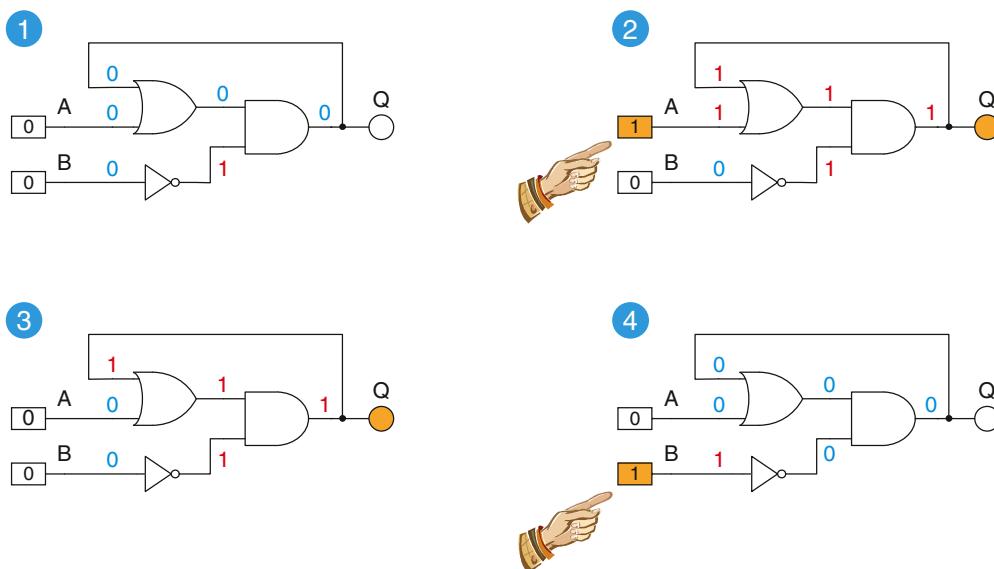

La señal de reloj no es más que un tren de pulsos de onda cuadrada, que trabaja con una frecuencia determinada. De esta señal se pueden utilizar sus valores o estados lógicos para sincronizar los circuitos secuenciales controlados con biestables. Así, el disparo con esta señal puede hacerse por nivel o por flanco.

- **Nivel:** es el valor lógico de la señal binaria que se mantiene en el tiempo y dura todo el semiciclo de la onda cuadrada. El nivel bajo es el 0 lógico y el nivel alto es el 1 lógico.

- **Flanco:** es una señal que detecta el instante en el que el valor lógico cambia de nivel. Así, se denomina flanco positivo, o ascendente, al que detecta el paso de nivel lógico bajo a nivel alto. Y flanco negativo, o descendente, el que detecta el paso de nivel alto a nivel bajo.

Figura 10.28. Formas de representar las señales de reloj en los bloques de los biestables.

## Saber más

En numerosas ocasiones, en los biestables, además de la salida  $Q$ , se representa una salida  $Q$  negada, cuyo estado es inverso a la anterior.

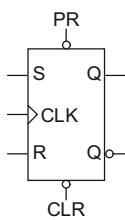

### 3.2. Biestable RS asíncrono

Todos los tipos de biestables se pueden analizar en su forma asíncrona y síncrona. No obstante, aquí solamente se estudiará el biestable RS con la forma de disparo asíncrona, ya que es el único de este tipo que tiene un interés práctico. Los restantes se estudiarán en función de su disparo mediante señales de reloj, o de forma síncrona.

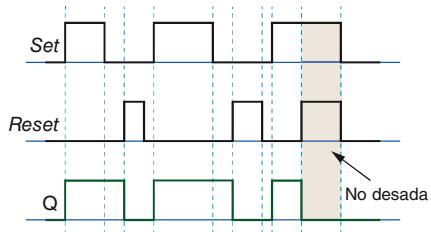

El biestable RS dispone de dos entradas, denominadas *set* y *reset*, una salida no negada denominada  $Q$ , y, en ocasiones, también una segunda salida negada respecto a la anterior llamada  $\bar{Q}$ . Así, cuando la entrada *set* es activada mediante un 1 lógico, la salida cambia también a 1.

Por el contrario, cuando la acción se produce sobre la entrada *reset*, la salida  $Q$  cambia al estado lógico 0. En este tipo de biestable, la detección de valor de las entradas no depende de otros tipos de señales como puede ser una de reloj.

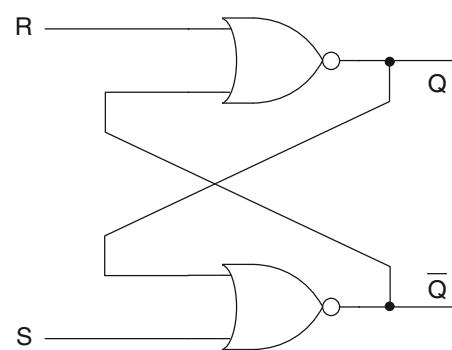

### 3.2.1. Biestable RS asíncrono con puertas NOR

Un biestable R-S puede configurarse con dos puertas NOR conectadas, como se muestra en la figura.

Figura 10.29. Cronograma biestable R-S asíncrono.

| R | S | Q              |

|---|---|----------------|

| 0 | 0 | Valor anterior |

| 0 | 1 | 1              |

| 1 | 0 | 0              |

| 1 | 1 | No deseado     |

Tabla de la verdad

Figura 10.30. Biestable RS con puertas lógicas NOR y tabla de la verdad.

En este circuito, sus entradas *set* y *reset* se activan por nivel lógico alto. Así, si el *set* está a 1 lógico, la salida se activa. Por el contrario, si es el *reset* el que lo está, la salida se desactiva. En el caso de que ambas estén a nivel bajo, la salida se mantiene en el estado anterior. Por otro lado, si se da el caso de que ambas entradas (*R-S*) están nivel lógico alto, nos encontramos en una situación no deseada, la cual debe evitarse, ya que se produciría un resultado incierto sobre la salida.

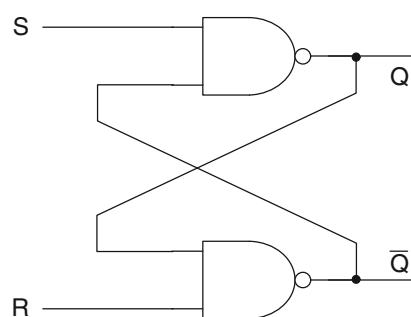

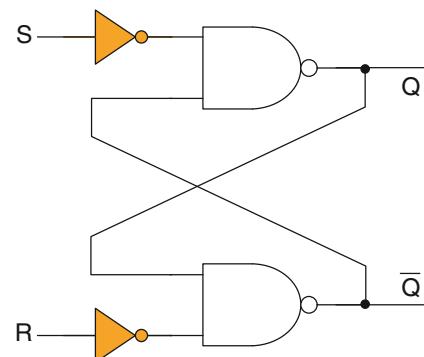

### 3.2.2. Biestable RS asíncrono con puertas NAND

Otra forma de configurar un biestable es mediante el circuito de la figura basado en puertas lógicas NAND. En este caso, las entradas *set* y *reset* funcionan por nivel lógico bajo, por lo que se puede decir que tiene un funcionamiento inverso a su homólogo con puertas NOR.

En este caso, la situación no permitida o no deseada se produce cuando las dos entradas se encuentran a nivel lógico bajo, es decir, a 0 lógico.

| R | S | Q              |

|---|---|----------------|

| 0 | 0 | No deseado     |

| 0 | 1 | 0              |

| 1 | 0 | 1              |

| 1 | 1 | Valor anterior |

Tabla de la verdad

Figura 10.31. Biestable RS con puertas lógicas NAND y tabla de la verdad.

Un biestable RS se representa habitualmente de forma simplificada mediante un rectángulo vertical, en el que en un lateral se representan las entradas y en el otro las salidas.

| Denominación           | Símbolo IEC | Símbolo ANSI | Identificador |

|------------------------|-------------|--------------|---------------|

| Biestable RS asíncrono |             |              | U             |

Tabla 10.5. Biestable RS asíncrono.

### 3.2.3. Biestables RS asíncronos en formato de circuito integrado

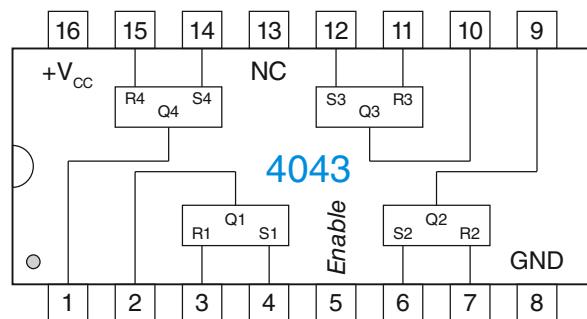

Existen varios modelos de circuitos integrados, tanto en tecnología TTL como en CMOS, que disponen de funciones biestables RS asíncronos. A continuación, se muestra el pinéado de los modelos 4033, basado en puertas NOR, y 4044, basado en puertas NAND.

Figura 10.33. Circuitos integrados 4043 y 4044 de biestables S-R basados en puertas NOR y NAND, respectivamente.

### Saber más

El biestable RS con puertas NAND puede trabajar con entradas de nivel lógico alto si se conecta en ellas una puerta inversora.

Figura 10.32. Biestable S-R con entradas a nivel lógico alto.

Figura 10.34. Biestable R-S síncrono de puertas NOR.

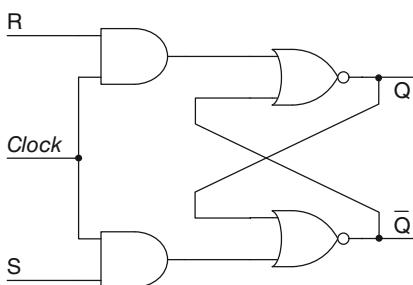

### 3.2.4. Biestables RS síncronos

Los biestables síncronos, además de atender a las señales de las entradas RS, dependen de una señal de reloj o de tren de pulsos, la cual puede realizar el disparo por nivel o por flanco.

La tabla de la verdad de un biestable RS síncrono es idéntica a la de un biestable síncrono, con la diferencia de que el resultado en la salida solamente se ejecuta cuando es evaluado el nivel o flaco correspondiente de la señal de reloj.

El cronograma y tabla de la de la siguiente figura muestran el funcionamiento de un biestable RS síncrono, cuyo disparo se hace por flanco negativo.

Tabla de la verdad

| CLK | R | S | Q              |

|-----|---|---|----------------|

| ↓   | 0 | 0 | Valor anterior |

| ↓   | 0 | 1 | 1              |

| ↓   | 1 | 0 | 0              |

| ↓   | 1 | 1 | No deseado     |

Figura 10.35. Cronograma biestable RS.

### Saber más

En ocasiones, los biestables síncronos disponen de dos entradas auxiliares que permiten actuar sobre el estado del biestable de forma síncrona, sin atender a señales de reloj. Estas suelen recibir los nombres de SET-RESET o PR-CLR, y suelen estar negadas.

Figura 10.36. Biestable síncrono con entradas auxiliares asíncronas.

Los símbolos para representar los biestables RS síncronos son los siguientes:

| Denominación                                  | Símbolo (IEC-ANSI) | Identificador |

|-----------------------------------------------|--------------------|---------------|

| Disparo por nivel (positivo y negativo)       |                    | U             |

| Disparo por flanco (ascendente y descendente) |                    | U             |

Tabla 10.6. Biestables RS síncronos.

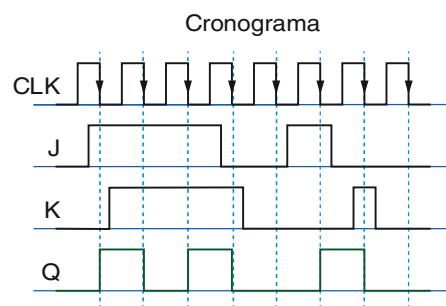

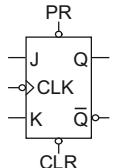

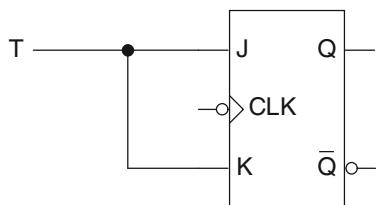

### 3.2.5. Biestable JK

Es posiblemente el biestable más utilizado, ya que corrige el problema de los RS cuando las dos entradas se encuentran en la situación no deseada. En este caso, la solución se consigue invirtiendo el valor de la salida respecto al estado anterior cada vez que se realiza el disparo con la señal de reloj.

Tabla de la verdad

| CLK | J | K | Q                          |

|-----|---|---|----------------------------|

| ↓   | 0 | 0 | Valor anterior             |

| ↓   | 0 | 1 | 0                          |

| ↓   | 1 | 0 | 1                          |

| ↓   | 1 | 1 | Cambia el estado contrario |

Figura 10.37. Cronograma biestable J-K.

### Saber más

En un biestable JK, la entrada J es la equivalente a la entrada S en los biestables RS, y la entrada K el equivalente a la R.

Disponen de varias entradas:

- J y K, para la activación y desactivación.

- CLK, para el tren de pulsos, que puede ser por nivel o por flanco.

- PR y CLR, entradas auxiliares, para el control asíncrono del biestable.

El símbolo del biestable JK es el siguiente:

| Denominación                               | Símbolo (IEC-ANSI)                                                                | Identificador |

|--------------------------------------------|-----------------------------------------------------------------------------------|---------------|

| Biestable JK (disparo por flanco negativo) |  | U             |

Tabla 10.7. Biestable JK.

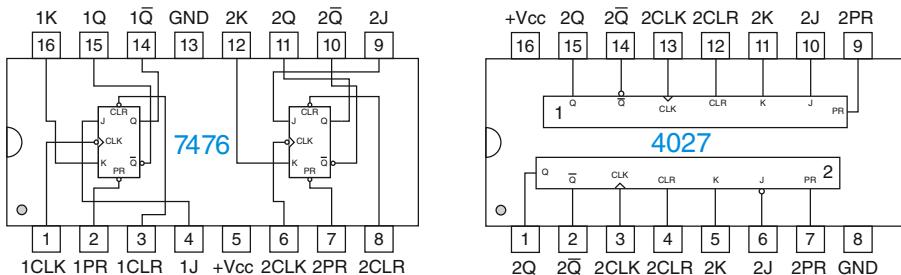

A continuación, se muestra el pineado de dos circuitos integrados, uno de la serie 40xx y otro de la serie 74xx, con la funcionalidad de biestables JK. Ambos disponen de un par de JK síncronos, con entradas auxiliares para control asíncrono.

Figura 10.38. Pineado de dos circuitos integrados con biestables J-K.

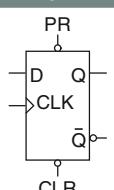

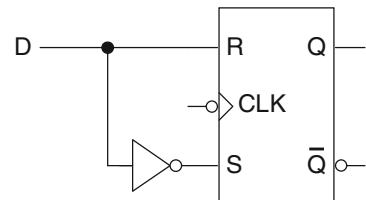

### 3.2.6. Biestable D

El biestable o *flip-flop* tipo D (dato) se configura a partir de un biestable RS síncrono en el que las dos entradas se conectan a un mismo punto (D), invirtiendo una de ellas respecto a la otra.

El biestable solamente dispone de una entrada para el dato y otra para la señal de reloj, la cual puede funcionar por nivel o por flanco.

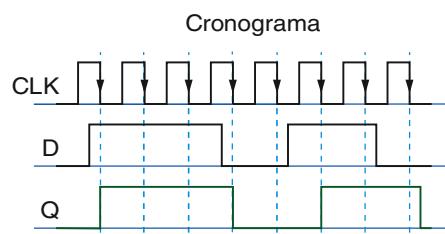

A continuación, se muestran la tabla de la verdad y el cronograma de un biestable D que funciona por flanco negativo.

Tabla de la verdad

| CLK | D | Q<br>(valor siguiente) |

|-----|---|------------------------|

|     | 0 | 0                      |

|     | 1 | 1                      |

Figura 10.40. Cronograma biestable D disparo por flanco negativo.

De igual forma que otros biestables síncronos, es habitual que disponga de dos entradas para su control asíncrono, denominadas PR y CLR.

El símbolo del biestable D es el siguiente:

| Denominación                              | Símbolo (IEC-ANSI)                                                                  | Identificador |

|-------------------------------------------|-------------------------------------------------------------------------------------|---------------|

| Biestable D (disparo por flanco positivo) |  | U             |

Tabla 10.8. Biestable D.

Figura 10.39. Circuito equivalente de un biestable D.

### Actividades

6. Localiza en internet la hoja de características del integrado 7474 y contesta a las siguientes preguntas:

- a) ¿Cuántos biestables tiene?

- b) ¿Cuál es su pineado?

- c) ¿Cómo es su disparo, por nivel o por flanco? ¿De qué tipo?

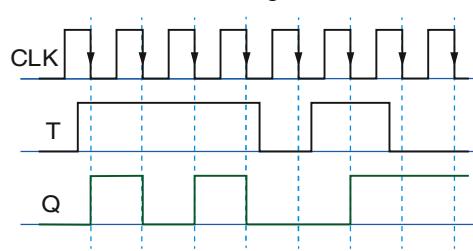

### 3.2.7. Biestable tipo T

Figura 10.41. Circuito de un biestable T tomando como base un JK.

El biestable tipo T se configura a partir de un biestable JK en el que se unen sus dos entradas en un único terminal denominado T (toggle).

En este caso, si la entrada T se mantiene a 0 lógico, no se produce cambio de estado en la salida. Sin embargo, cada vez que T cambia a nivel lógico alto, la salida invierte su estado una vez evaluado el flanco de la señal de reloj.

Tabla de la verdad

| CLK | Q<br>(previo) | Q<br>(valor siguiente) |

|-----|---------------|------------------------|

| 0   | 0             | 0                      |

| 0   | 1             | 1                      |

| 1   | 0             | 1                      |

| 1   | 1             | 0                      |

Cronograma

Figura 10.42. Cronograma biestable T con disparo por flanco negativo.

El símbolo del biestable T es el siguiente:

| Denominación                              | Símbolo (IEC-ANSI) | Identificador |

|-------------------------------------------|--------------------|---------------|

| Biestable T (disparo por flanco negativo) |                    | U             |

Tabla 10.9. Biestable T.

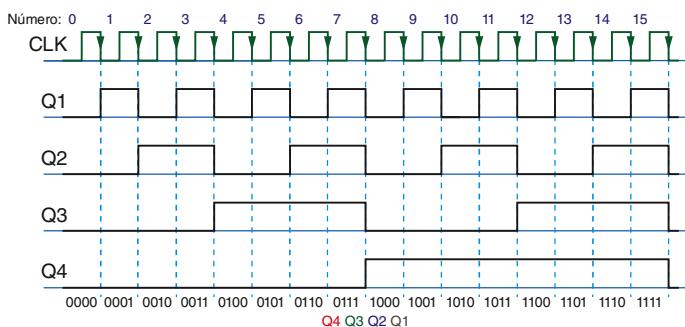

### 3.3. Contadores

Los contadores son circuitos digitales secuenciales que se forman a partir de biestables. Con ellos es posible contabilizar pulsos producidos en su entrada, y sincronizados con la señal de reloj.

Un contador es un circuito con memoria que permite almacenar datos codificados en binario, para posteriormente ser utilizados en otras partes del circuito y actuar en consecuencia.

Figura 10.43. Cronograma de un contador binario.

Figura 10.44. Contador binario basado en biestables J-K.

Los contadores pueden ser ascendentes o descendentes, en función de si el impulso en su entrada incrementa o decrementa el número codificado en su salida.

También pueden ser síncronos o asíncronos, si la comutación se hace en función de una señal de reloj o no.

El número máximo que se puede contar depende de la cantidad de salidas utilizadas para codificar el número en binario. Así, con dos salidas ( $2^2$ ) se puede contar de 0 a 3, con tres salidas ( $2^3$ ) de 0 a 7, y así sucesivamente.

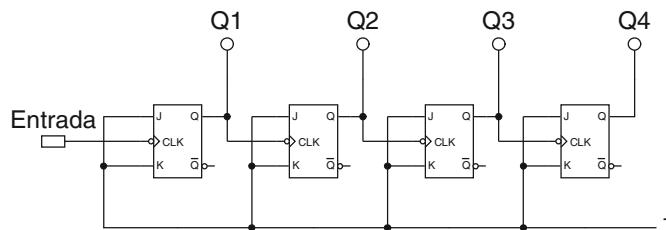

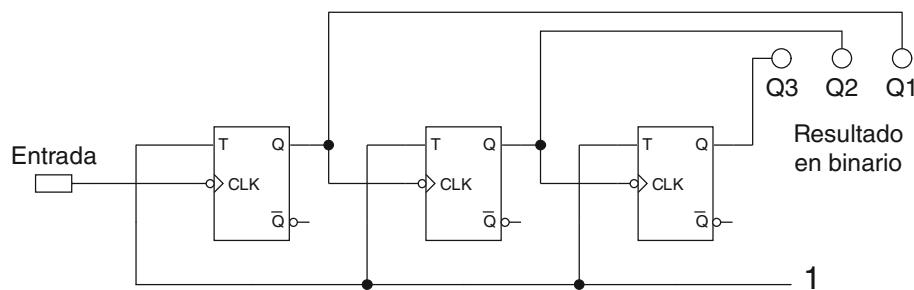

### 3.3.1. Contador asíncrono binario

En este tipo de contador, los pulsos se introducen manualmente mediante una fuente externa, como puede ser algún tipo de sensor o elemento de conmutación. Así, cada vez que se detecta el flanco de dicha señal, se produce el cálculo en el circuito.

En este tipo de contadores, los biestables se conectan en cascada, uniendo la salida Q de un biestable con la entrada CLK del siguiente.

En la figura se muestra un contador binario de 3 bits de tipo ascendente, configurado en base a biestables tipo T.

Figura 10.45. Contador binario asíncrono ascendente (UP).

Con este contador, cada vez que se produce un flanco negativo en la entrada, el contador se incrementa en uno. El resultado se obtiene en binario y, como Q1 es el bit menos significativo, es necesario ordenar las salidas para hacer la lectura correcta.

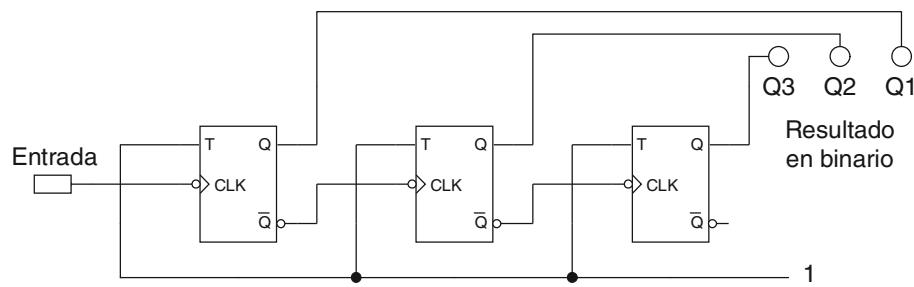

También es posible configurar el contador para que sea de tipo descendente, de forma que cada vez que es detectado el flanco de entrada, el contador disminuya su valor.

Figura 10.46. Contador binario asíncrono descendente (DOWN).

En este caso, las salidas no negadas de cada biestable son cada uno de los bits correspondientes del número a codificar, y la salida Q inversa es la que se conecta en cascada con los demás biestables.

### Seguridad

El uso de sensores externos de tipo electromecánico para activar los contadores, como pueden ser pulsadores o interruptores, requiere utilizar circuitos antirrebotes, como los estudiados en la unidad anterior, ya que de otra manera la conmutación mecánica puede producir varios pulsos en una sola acción.

## Actividades

7. Utilizando un software de simulación electrónica, monta el circuito del contador binario asíncrono ascendente de 3 bits, basado en biestables T. Conecta un pulsador lógico a la entrada y comprueba su funcionamiento.

8. Basándote en el circuito de la actividad anterior, ¿qué tendrías que hacer para que el contador tenga 4 bits? ¿Qué rango de números se podría contar? Dibuja el circuito en el simulador y comprueba su funcionamiento.